doi: 10.3969/j.issn.1006-1576.2012.02.016

# 基于 FPGA 的 SDRAM 控制器设计方案

侯宏录, 张文芳

(西安工业大学光电工程学院,西安 710032)

摘要:针对高速实时图像采集系统中数据量大需要缓存的问题,提出一种基于 FPGA 的 SDRAM 控制器设计方案。在分析 SDRAM 基本操作原理的基础上,通过引入状态机和仲裁机制,利用 Verilog 语言在 QuartusII 的开发环境中进行设计输入与仿真验证,实现了高速数据的缓存和传输。详细介绍各模块的具体设计方法以及整体设计的实现过程。实验测试结果表明:该控制器设计灵活、工作稳定可靠,成本低廉,可作为 IP 核应用于不同 SOC 的高速缓存系统中。

关键词: 控制器; SDRAM; FPGA; Verilog 中图分类号: TP332 文献标志码: A

## Design Scheme of SDRAM Controller Based on FPGA

## Hou Honglu, Zhang Wenfang

(School of Optoelectronics Engineering, Xi'an Technological University, Xi'an 710032, China)

**Abstract:** Aiming at the problem of large-capacity data, need memory cache in high-speed real-time image processing system, a new SDRAM controller based on FPGA was proposed. Based on the analysis of the basic operation principle of SDRAM, through introducing the state machine and arbitration mechanism, the purpose of high-speed data cache and transmission is realized by carrying on the design input and simulation validation in QuartusII development environments using Verilog language. This paper introduces the specific design of each module and the realization of the whole design in detail. The test results show that the controller designed is flexible, stable, reliable, low cost, and can be used as IP core in different SOC high-speed cache system.

Key words: controller; SDRAM; FPGA; Verilog

## 0 引言

在嵌入式高速图像采集和存储系统中,由于前段采集和后端存储转发的速度不同,常常需要用到存储容量大、读写速度快的缓存器<sup>[1]</sup>。目前构成缓存的芯片主要有:双口 RAM、FIFO、SRAM、SDRAM等。一般双口 RAM 和 FIFO 的速度及容量都较小,不适合于图像数据的缓存。SRAM 读写速度快,控制简单,但容量小、成本高。而 SDRAM 具有存贮容量大、传输速度快、价格低廉、支持突发读写等优点,因此成为图像缓存的首选存储介质<sup>[2]</sup>。

现今大多数系统采用专用芯片实现 SDRAM 的控制电路,灵活性较差,不利于 SDRAM 的特殊应用。 因此设计可移植、通用性强的 SDRAM 控制器软核成为大容量、高速图像数据缓存中的关键问题<sup>[3]</sup>。

FPGA 具有运行速度快、可重复编程、集成度高等优点,是进行原始设计最理想的载体<sup>[4]</sup>。为此,笔者以高速数据通信中数据缓存为应用背景,提出一种采用 Verilong 语言编程的通用 SDRAM 控制器的

FPGA 模块化解决方案。

## 1 SDRAM 的基本内部操作和工作时序

本设计采用台湾力晶公司的 SDRAM 芯片 A2V64S40CTP-G7, 其容量为 8 MB (1M×16bits×4banks)。

#### 1.1 SDRAM 的基本内部操作

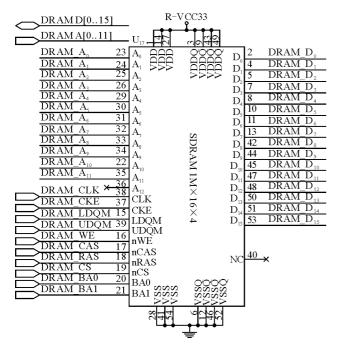

A2V64S40CTP-G7采用 54 引脚的 TSOP 封装, 其芯片信号主要分为地址信号、数据信号和控制信 号 3 类<sup>[5]</sup>,并且采用同步接口方式与系统时钟同步, 其芯片管脚如图 1(图中, X 代表未使用引脚)所示。

地址信号为: DRAM\_BA[1:0], DRAM\_A[11:0]。 DRAM\_BA[1:0]用于页选择,DRAM\_A[11:0]用于行、列地址选择,通过分时复用决定是行地址还是列地址。在读写操作中,在地址线上依次给出页地址、行地址、列地址,最终确定存储单元地址。

数据信号为 DRAM\_D[15:0],是双向数据信号, 且有效与否受输入输出使能信号 DRAM\_LDQM 和 DRAM UDQM 的控制。

收稿日期: 2011-09-01; 修回日期: 2011-10-24

基金项目: 陕西省科学技术研究发展计划项目(2011K06-22)

作者简介: 侯宏录(1960一), 男, 陕西人, 博士, 教授, 从事光电测试, 信息融合, 复杂系统建模、仿真与作战效能评估研究。

图 1 SRRAM 芯片管脚图

控制信号为: DRAM\_CKE, DRAM\_LDQM, DRAM\_UDQM, DRAM\_WE, DRAM\_CAS, DRAM\_RAS, DRAM\_CS。DRAM\_CKE 用于时钟使能, DRAM\_LDQM 和 DRAM\_UDQM 用于掩码, 也即输入输出使能, DRAM\_CS 用于片选, DRAM\_CAS, DRAM\_RAS, DRAM\_WR 用于操作控制,具体操作指令见表 1。(表中, H 代表高电平, L 代表低电平, X 代表任意电平)

表 1 SDRAM 基本操作命令

| 命令行(功能)                           | CS# | RAS# | VSD# | WE# | DOM | 地址线        | DQs    |

|-----------------------------------|-----|------|------|-----|-----|------------|--------|

| 明令令禁止(NOP)                        | Н   | X    | X    | X   | •   | X          | X      |

| 无操作(NOP)                          | L   | Н    | Н    | Н   | X   | X          | X      |

| 有效/活动(使指定<br>L-BANK 中的指定行有效)      | L   | L    | Н    | Н   | X   | BANK/<br>行 | X      |

| 读取(使指定 L-BANK<br>中的指定列开始读取数<br>据) | L   | Н    | L    | Н   | L/H | BANK/列     | X      |

| 写入(使指定 L-BANK<br>中的指定列开始写入数<br>据) | L   | Н    | L    | L   | L/H | BANK/列     | 有效     |

| 突发终止传输                            | L   | Н    | Н    | L   | X   | C          | 活<br>动 |

| 预充电(关闭指定或全部 L-BANK 中的工作行)         | L   | L    | Н    | L   | X   | 相应编码       | X      |

| 自动刷新或自刷新(后<br>者进入自刷新模式)           | L   | L    | L    | Н   | X   | X          | X      |

| 模式寄存器加在(写入)                       | L   | L    | L    | L   | X   | 操作码        | X      |

| 写允许/输出允许                          | _   | _    | _    | _   | L   | _          | 有效     |

| 写 禁止 / 输 出 屏 蔽<br>(Bigh-Z)        | _   | _    | _    | _   | В   | _          | 屏蔽     |

#### 1.2 SDRAM 的工作时序

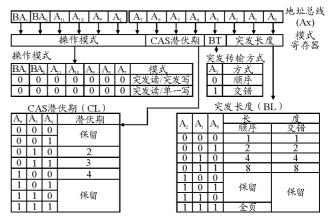

SDRAM 在每次开机进入正常工作状态之前,需要进行芯片的初始化,依次为: 200 μs 输入稳定期,所有 L-BANK 的预充电,8 个刷新周期和模式寄存器设置(MRS),其关键在于模式寄存器的设置,用于设定 SDRAM 的操作模式,CAS 潜伏期,突发方式和突发长度。当 SDRAM 进入 MRS 时,地址线上即为 MRS 操作码,具体参数设置如图 2。

图 2 SDRAM 模式寄存器设置

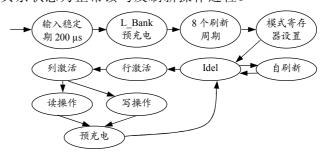

在设置 MR 之后,SDRAM 开始进入正常工作状态。首先激活将要读写的行,然后使列选通,之后对该地址进行突发读写。另外,由于 SDRAM 存储结构的特殊性,当读写操作完成并对新的一行寻址时,需要对原有效行中所有存储体进行数据重写,并对行地址复位,即预充电<sup>[6]</sup>。

SDRAM 控制器以状态机的形式实现,其状态机原理如图 3<sup>[7]</sup>所示。其中,从输入稳定期到模式寄存器设置环节为 SDRAM 上电后的初始化过程,其余状态为正常读写及刷新操作过程。

图 3 SDRAM 控制器状态机

#### 2 SDRAM 控制器的设计

#### 2.1 总体设计框图

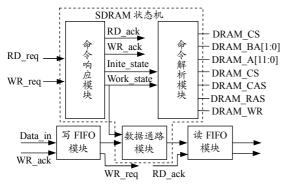

在高速数据通信系统中,数据输入模块与数据输出模块之间主要有数据缓存(写 FIFO,读 FIFO)模块和 SDRAM 控制器组成,读写 FIFO 通过

QUARTUS 2 中 IP 核例化得到, SDRAM 控制器通过有限状态机和仲裁机制来实现数据读写功能。其缓存原理框图如图 4<sup>[8]</sup>所示。

图 4 SDRAM 缓存原理框图

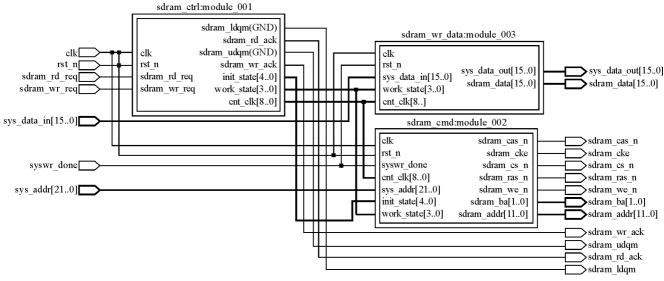

在这里,各模块之间通过锁相环 PLL 解决时钟同步问题。虚线框内为 SDRAM 控制器,包括命令响应、命令解析、数据通路共 3 个模块<sup>[9]</sup>。以下分模块进行介绍。

#### 2.2 命令响应模块

命令响应模块用于响应外部读写要求并产生 状态指令给命令解析模块, 其状态分为初始化状态 (Inite state)和工作状态(Work state)2 类。初始化 状态包括:空操作状态(I NOP),预充电状态 (I PRE), 8 次自刷新状态(I AR1~8), 模式寄存 器设置状态(I MRS)和初始化完成状态(I DONE)。 各状态过渡均通过定时器依据 SDRAM 电气特性完 成。这里取 SDRAM (A2V64S40CTP-G7) 每隔 15 us 刷新一次,其依据为其存储体中电容的数据有效保 存期上限为 64 ms, 刷新命令一次对一行有效, 而 其每页有 4 096 行, 因此刷新速度应快于 64 ms/4 096=15.6 μs, 这里取 15 μs。工作状态包括: 空闲状态(W IDLE),自刷新状态(W AR),行选通 状态(W ACTIVE), 行选通周期状态(W TRCD), 读数据状态(W READ),读潜伏期状态(W CL),N 个数据读出期状态(W RD),读后预充电状态 (W RWAIT), 写数据状态(W RITE), N 个数据写 入期状态(W WD), 写回状态(W TDAL)。由于本 模块状态较多, 因此采用状态机形式实现各状态功 能,其状态机如图2所示。

## 2.3 命令解析模块

命令解析模块用于接收状态指令并生成合适的操作命令给 SDRAM 器件。SDRAM 指令较多,主要分初始化指令、刷新指令和读写指令 3 类,这里引入仲裁机制。初始化操作是 SDRAM 正常工作

的基础,所以它的优先级最高,刷新请求的优先级 次高,读写请求的优先级最低。当某一种操作正在 执行时不会响应后来的请求。

为实现命令解析功能,模块采用 verilog 语言,设 定 控 制 指 令 字(sdram\_cmd)等 于(DRAM\_CKE,DRAM\_CS,DRAM\_RAS,DRAM\_CA S,DRAM\_WE),当 SDRAM 处于上述命令响应模块描述的状态时,根据仲裁的结果和 SDRAM 控制器模式寄存器对工作模式参数的设置,结合表 1 所述 SDRAM 基本操作命令,分别对各状态进行译码,译码的结果就是输出的控制指令字。

## 2.4 数据通路模块

数据通路模块用于处理读写命令时的数据传输操作,控制数据以适当时序进行有效输入输出[11]。根据寄存器的设置及指令译码的结果对把系统非复用的地址处理为 SDRAM 复用的地址,使得 SDRAM 的地址及数据和相应的操作指令在时序上同步。该模块为 FPGA 主控制器和 SDRAM 器件之间提供了数据通道。当 SDRAM 处于突发写操作状态时,数据由 Data\_in 总线进入模块; 当 SDRAM 处于突发读操作状态时,数据由 Data out 总线输出。

## 3 FPGA设计实现及时序特性

笔者用 Verilog 语言在 Quartus 9.1 的开发环境中进行了设计输入与综合仿真,并将设计代码下载到 Cyclonell EP2C35F672C6 的 FPGA 上。为了验证设计的正确性,通过 modelsim 工具对 SDRAM 的工作状况进行仿真验证<sup>[12]</sup>,图 5、图 6 和图 7 分别为 SDRAM 在初始化,突发写,突发读时的工作时序。从时序图中可以看出,初始化过程中,控制器依次发出了 200 μs 空闲状态,预充电,8 个刷新周期和模式寄存器设置;在写过程中,依次发出行激活、TRCD、写、突发 8 位和写回操作;在读过程中,依次发出行激活、TRCD、读、读潜伏、突发 8 位和预充电操作。各种控制信号完全满足时序要求,各种状态能有效进行跳转,并有效实现了 SDRM 的初始化和读写操作。

图 5 SDRAM 初始化时序

图 6 SDRAM 写时序

图 7 SDRAM 读时序

图 8 SDRAM 控制器模块 RTL 级视图

通过以上时序分析验证了设计的正确性,将代码下载到 FPGA,经编译得到的 SDRAM 控制器模块 RTL 级视图如图 8 所示。

其中,sdram\_ctrlmodule\_001 为命令响应模块,sdram\_cmdmodule\_002 为命令解析模块,sdran\_wr\_datamodule\_003 为数据通路模块。经与缓存原理框图图 3 对照可知,通过上述各模块的详细设计,成功实现了 SDRAM 控制器的各种功能。

## 4 结束语

笔者设计了一种基于 FPGA 的高速数据采集系统中的 SDRAM 控制器,采用 verilog 语言,在ALTERA 公司的 FPGA (EP2C35F672C6) 芯片上成功实现了 SDRAM 控制器的功能。利用 FPGA 实现SDRAM 控制器,不仅可以根据实际需求灵活进行配置,降低专用集成电路的设计风险,而且具有电路简单、工作可靠等优点。该技术同样可以作为 IP核应用于不同的 SOC 数据缓存与传输系统中,有助于大大缩短产品的开发周期。

#### 参考文献:

[1] . 基于 FPGA 的 SDRAM 控制器设计及应用[D]. : 大 , 2007.

- [2] , . 使用 Verilog 实现基于 FPGA 的 SDRAM 控制器[J]. 电 , 2005(1): 53-55.

- [3] 效 . 高 进 -终 存 指 [EB/OL]. [2002-12-17].http://wenku.baidu.com/view/c81237ea81c7 58f5f61f67c2.html.

- [4] 一 , . 基于 FPGA 的 SDRAM 控制器 设计[J]. 电 工程 , 2003, 29(9): 10-13.

- [5] , 图像 理系统中 SDRAM 控制器的 FPGA 实现[J]. 计 机 (入式与 SOC), 2009, 25(52): 164-165

- [6] , 灵 , 基于 FPGA 的 与 部 SDRAM 通 的电路设计[J]. 电 测量 ,2006, 25(1): 14-16.

- [7] ,张宏 . 使用 FPGA 操作 SDRAM 的 RTL 码 实现[J]. 表 , 2006, 3: 52-53.

- [8] , 文 , 新 . 一种 SDRAM 控制器 核的 Verilog 设计[J]. 电 ,2003,8(4):89-93.

- [9] , , 基于 FPGA 的 SDRAM 控制器设计与实现[J]. 电 , 2003, 208(1): 8-12.

- [10] , , , 程 . 实时 SDRAM 控制器 的 FPGA 设计与实现[J]. 原理工大 , 2006, 37: 5-8

- [11] 传 ,高 ,张 . 一种 的 SDRAM 控制器实现 [J]. 计 机与数 工程, 2010, 28(8): 197-199.

- [12] 宏 , . . 一种用于高速数据采集的 SDRAM 控制器[J]. 题 与工程应用, 2010, 40(4): 62-64.